## 2020年 演算増幅器設計コンテスト発表会

#### 2020年12月3日

## 発表会プログラム

・ 上位入賞者作品解説(シミュレーションの部)

|       |              | 部門1 | 部門2 | 部門3 | 部門4 |

|-------|--------------|-----|-----|-----|-----|

| 14:05 | 加藤博己(群馬大学)   | 3位  | 4位  |     |     |

| 14:15 | 今野哲史(群馬大学)   |     | 3位  | 4位  |     |

| 14:25 | 岡本憲典(有明高専)   | 7位  | 6位  |     | 奨励賞 |

| 14:40 | 日比彪斗(愛知工業大学) | 6位  |     | 2位  |     |

| 14:55 | 休憩           |     |     |     |     |

| 15:10 | 齋藤滉生(東京理科大学) | 1位  |     |     |     |

| 15:25 | 川原啓輔(東京理科大学) |     | 5位  | 5位  | 1位  |

| 15:50 | 猿田将大(群馬大学)   | 5位  | 1位  | 3位  |     |

| 16:15 | 齋藤彰寛(群馬大学)   |     | 2位  | 1位  | 奨励賞 |

| 16:40 | 講評(兵庫審査委員長)  |     |     |     |     |

# 協賛企業

- セイコーNPC株式会社

- ・ エイブリック株式会社

- ・ 旭化成エレクトロニクス株式会社

- · 株式会社東芝

- · 横河電機株式会社

- ・ ダイアログ・セミコンダクター株式会社

- · 新日本無線株式会社

- ・ ルネサスエレクトロニクス株式会社

# 演算増幅器設計コンテスト 部門1 3位 部門2 4位

群馬大学 理工学部 電子情報理工学科 学部4年 加藤博己

#### MOSのwidth[um]と抵抗値[MΩ] (lengthは全て0.2um)

| M1  | M2  | М3   | M4  | M5  | M6  | М7  | M8  | М9  |

|-----|-----|------|-----|-----|-----|-----|-----|-----|

| 0.9 | 0.3 | 15.5 | 0.9 | 0.9 | 0.3 | 0.3 | 0.9 | 0.9 |

| M10 | M11 | M12  | M13 | M14 | M15 | M16 | R1  | R2  |

| 0.3 | 0.3 | 39.5 | 1.2 | 0.3 | 1.9 | 0.8 | 20  | 12  |

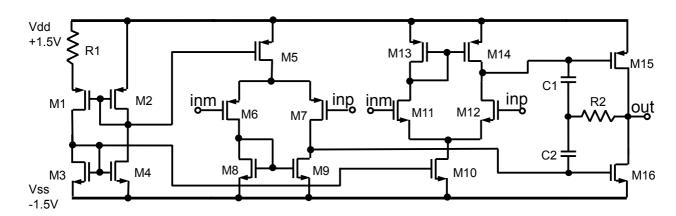

Vdd = 1.5V, Vss = -1.5V PMOSバルクは全てVDD NMOSバルクは全てVSS

GUNMA UNIVERSITY TAKAI-LAB

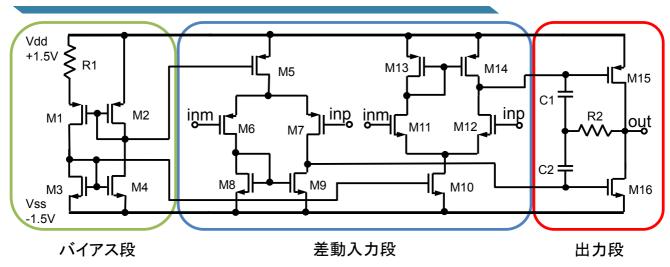

#### 設計方針

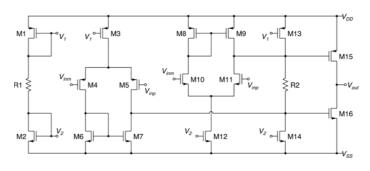

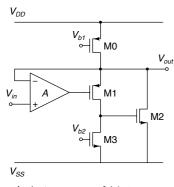

#### <回路構成>

- バイアス段電流パスを少なくし、 消費電流を抑える。

- 入力段 pmos, nmos入力により スルーレートを向上させ、 入力電圧範囲を広げる。

- ●出力段

- ・プッシュプル動作により、スルーレートを向上させる。

- ・バイアス電位を固定させて安定性を向上させる。

#### 設計方針

#### <素子值>

- スルーレートを向上させるため に、小さいL、Wの値を用いる。

- スルーレートを向上させるために テール電流源に相当する MOS(M3, M12)のWを大きくする。

- 消費電流を少なくするために抵抗の値を大きくする。

| MOSのwidth[um]と抵抗値[MΩ] |     |      | [ΜΩ] | (leng | sth(は全 | ₹70.2i | ım) |     |

|-----------------------|-----|------|------|-------|--------|--------|-----|-----|

| M1                    | M2  | МЗ   | M4   | M5    | M6     | M7     | M8  | M9  |

| 0.9                   | 0.3 | 15.5 | 0.9  | 0.9   | 0.3    | 0.3    | 0.9 | 0.9 |

| M10                   | M11 | M12  | M13  | M14   | M15    | M16    | R1  | R2  |

| 0.3                   | 0.3 | 39.5 | 1.2  | 0.3   | 1.9    | 0.8    | 20  | 12  |

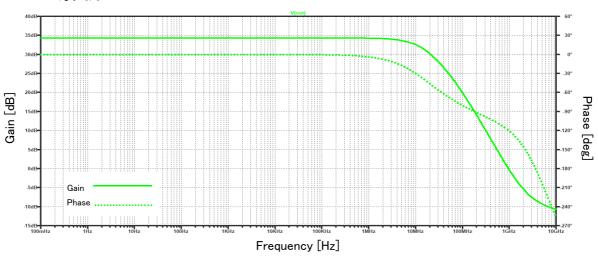

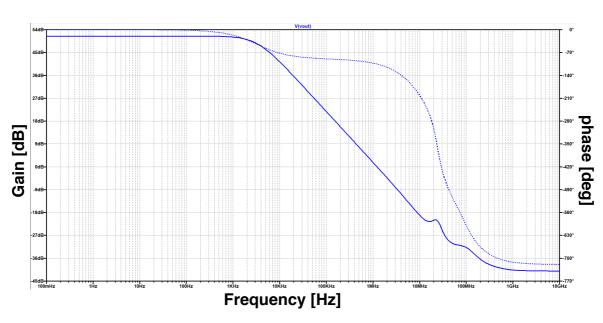

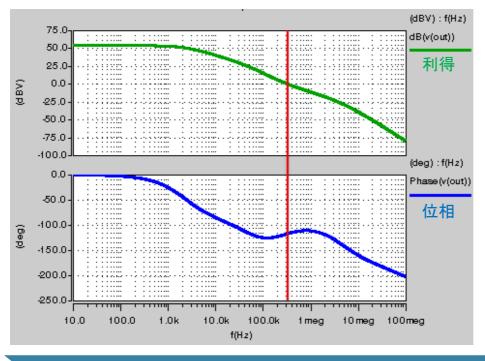

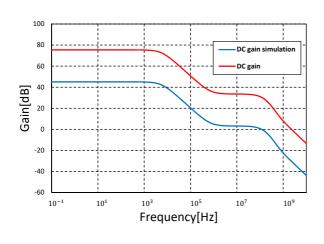

#### シミュレーション結果

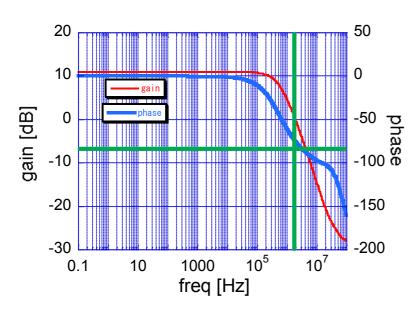

#### AC解析

シミュレーションによる直流利得 : 34.3 dB

位相余裕: 60.2 deg

シミュレーションによる出力抵抗 : 719 Ω

GUNMA UNIVERSITY TAKAI-LAB

直流利得:64.3 dB 出力抵抗 : 610k Ω

#### シミュレーション結果

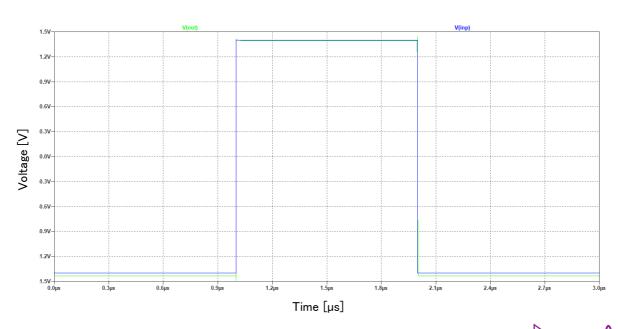

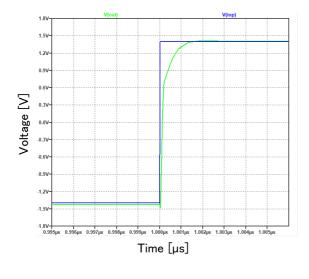

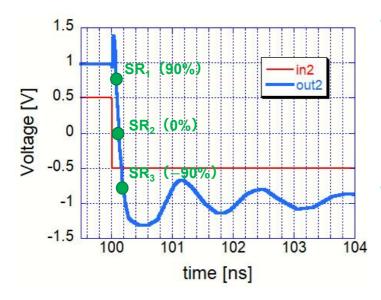

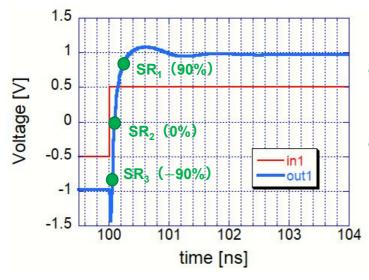

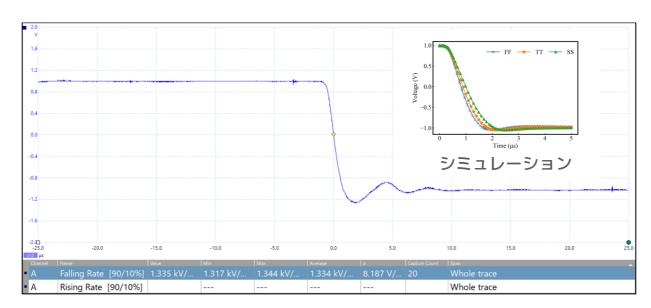

#### 過渡解析(スルーレート)

## シミュレーション結果

#### 過渡解析(スルーレート)

立ち上がり : 1.07e+010 V/s

立ち下がり: 1.22e+010 V/s

GUNMA UNIVERSITY TAKAI-LAB

#### シミュレーション結果

#### 消費電流

回路全体: 7.46 μA

GUNMA UNIVERSITY TAKAI-LAB  $\longrightarrow 8$

#### 評価結果

| 項目     | 評価結果           |

|--------|----------------|

| スルーレート | 2.2947E+10 V/s |

| 消費電流   | 7.2828E-06 A   |

| 同相入力範囲 | 1.0000E+02 %   |

| 直流利得   | 6.3475E+01 dB  |

| スコア    | 2.0000E+19     |

#### 最後に

- 設計をしていく上で考慮しなければならない点などを学べる、良い経験となった。

- 設計を通して深く考えることで、回路について 学ぶ良い機会にもなった。

#### 謝辞

協賛企業の皆様及び運営の皆様に心 より感謝申し上げます。

## 2020年演算増幅器設計コンテスト

部門2 3位 部門3 4位

群馬大学 修士2年 今野 哲史

1

#### はじめに

#### なるべく簡潔に設計

- 〇 昨年設計した自分の回路構成を利用

- MOSのパラメータが昨年と変わったので調整

#### 評価式と設計方針

部門2の評価式

#### 利得帯域幅積 × 位相余裕

#### 消費電力<sup>2</sup> × 出力抵抗 × 入力換算雑音

回路の設計方針

- 出力抵抗は0.1Ω

- () 消費電力を下げる

- 〇 入力換算雑音を下げるためにPMOS入力

- 利得帯域幅積と位相余裕はトレードオフ なので、今回は気にしない

**GUNMA UNIVERSITY TAKAI-LAB**

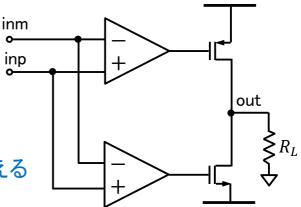

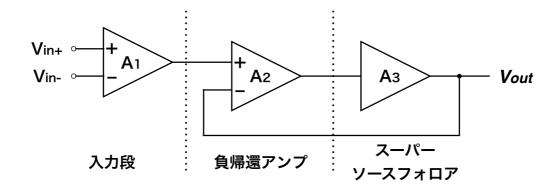

#### 設計方針

出力抵抗を下げる

- 負帰還 + スーパーソースフォロワ (SSF)

- ・SSFの出力抵抗

$$R_{OUT} = \frac{1}{g_{m2}g_{m4}r_{o2}}$$

→ カスコード接続にすることで更に出力抵抗を下げる

• 負帰還

増幅器の利得A倍だけ出力抵抗が低下

$$R_{OUT} = \frac{1}{Ag_{m2}g_{m4}r_{o2}}$$

GUNMA UNIVERSITY TAKAI-LAB  $\longrightarrow 4 \longrightarrow 4$

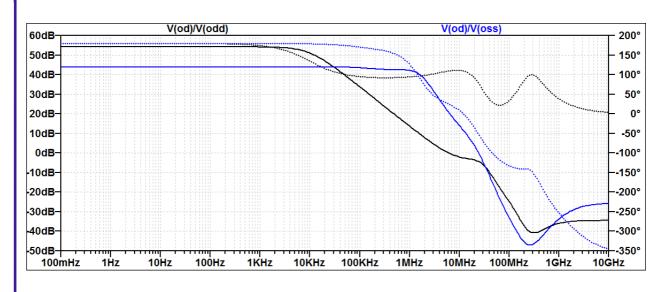

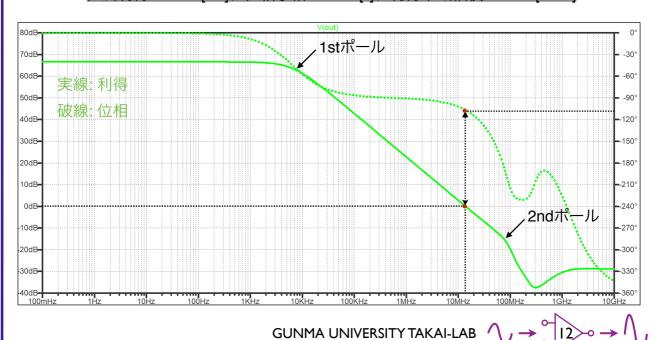

#### AC解析結果: 利得帯域幅積·位相余裕

**GUNMA UNIVERSITY TAKAI-LAB**

0.4 / 10.0

300

1.5

直流利得 : 51.5 dB 利得帯域幅積 : 1.24 MHz 位相余裕 : 74.5 deg

**GUNMA UNIVERSITY TAKAI-LAB**

#### 結果

#### 提出回路のスコア

| 項目     | 評価結果       | 単位  |

|--------|------------|-----|

| 消費電力   | 3.3251e-05 | W   |

| 出力抵抗   | 1.6577e-01 | Ω   |

| 入力換算雑音 | 5.2595e-03 | V   |

| 利得带域幅積 | 1.2225e+06 | Hz  |

| 位相余裕   | 7.4717e+01 | deg |

| スコア    | 9.4756e+19 |     |

| ネットリスト | 見る         |     |

| 回路図    | 見る         |     |

**GUNMA UNIVERSITY TAKAI-LAB**

#### 終わりに

- - )出力抵抗を小さく設計することで、 入賞する回路が設計できた。

- O スコアを向上させるためには

- ・出力抵抗を0.1Ω以下(コンテストでは0.1Ωが最低値)にする

- ・トレードオフに含まれない入力換算雑音を改善する

- ・利得帯域幅積を完全する

- ・消費電力を削減する

この様な貴重な機会を与えて下さった 協賛企業の皆さまと運営の皆様に深く感謝を申し上げます

# ご静聴ありがとうございました GUNMA UNIVERSITY TAKAI-LAB ◇→。9→・→

## 演算増幅器設計コンテスト

部門1:7位 部門2:6位

部門4:奨励賞

令和 2 年 12 月 3 日

有明工業高等専門学校 National Institute of Technology, Ariake College

報システム工学専攻 2年 石川研究室 岡本 憲典

Copyright © 2020 ICLab. All Rights Reserved.

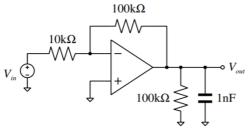

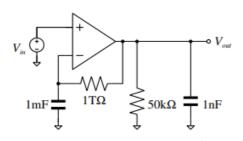

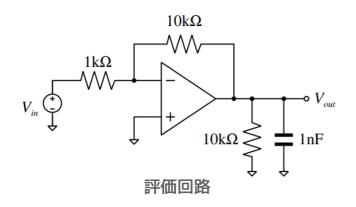

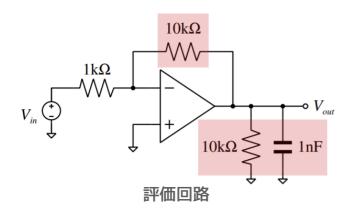

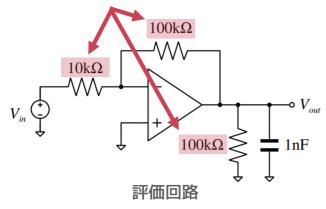

部門4:要件

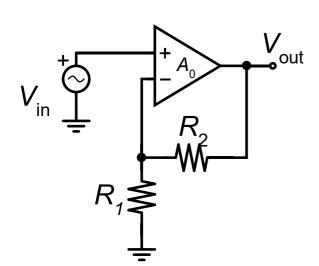

評価:(a)に示す利得が-10倍の反転増幅回路における無信号時の 消費電力

(a): デザイン部門の評価回路

(b): 小信号評価回路

| 項目     | 要件         | 備考  |

|--------|------------|-----|

| 電源電圧   | 3V (±1.5V) | 固定  |

| 直流利得   | 40dB以上     | (b) |

| 位相余裕   | 45°以上      | (b) |

| 帯域幅    | 20kHz以上    | (a) |

| 入力電圧範囲 | ±0.1V以上    | (a) |

| スルーレート | 1V/µs以上    | (a) |

要件を満たし、低消費電力化

部門4:設計方針

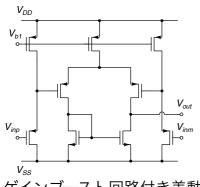

入力段を2つ用いてAB級動作

スルーレート改善

出力段にAB級出力回路を用いる

無信号時の消費電流を抑える

ゲート幅 W

$$W_n = L \times (5 \sim 10)$$

$W_p = W_n \times (2 \sim 2.5)$ が目安

出典:LSI設計常識講座

https://www.youtube.com/channel/UCKIKdQ0bGHmPwyHqJYIzZpQ/videos

Copyright © 2020 ICLab. All Rights Reserved.

2/11

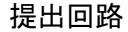

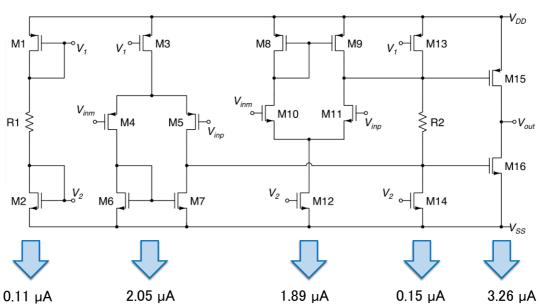

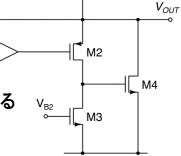

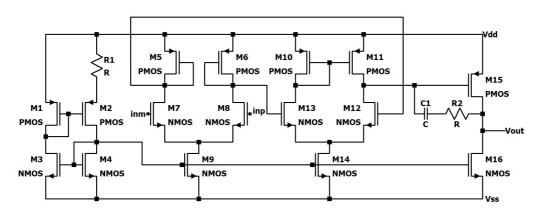

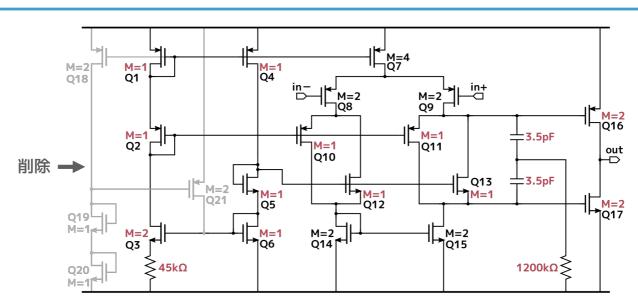

## 部門4:提出回路

バイアス段:電源電圧不感型カレントミラー

差動入力段: プッシュプル回路

出力段: AB級出力回路

## 部門4:提出回路

| 素子値<br>[µm] | M2~4 , M6~9<br>M11~14 | M5 , M10       | M1, M15, M16   |

|-------------|-----------------------|----------------|----------------|

| PMOS        | 10.0 / 0.6            | 10.0 / 0.6 × 2 | 10.0 / 0.6 × 4 |

| NMOS        | 5.0 / 0.6             | 5.0 / 0.6 × 2  | 5.0 / 0.6 × 3  |

|             | 素子值 |

|-------------|-----|

| R1 [kΩ]     | 62  |

| R2 [kΩ]     | 385 |

| C1 ,C2 [pF] | 1.0 |

PMOSのバルクは全てVDD、NMOSのバルクは全てVSSに接続

Copyright © 2020 ICLab. All Rights Reserved.

4 /11

#### シミュレーション

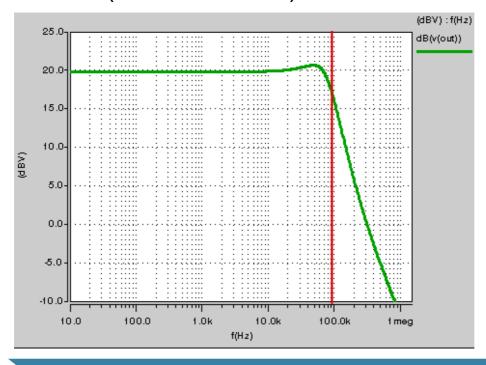

## 直流利得,位相余裕(評価回路b:AC)

直流利得 53.7365 [dB] 位相余裕 63.3172 [deg]

## シミュレーション

#### 帯域幅 (評価回路a:AC)

−3dB帯域幅 93.7 [kHz]

Copyright © 2020 ICLab. All Rights Reserved.

6 /11

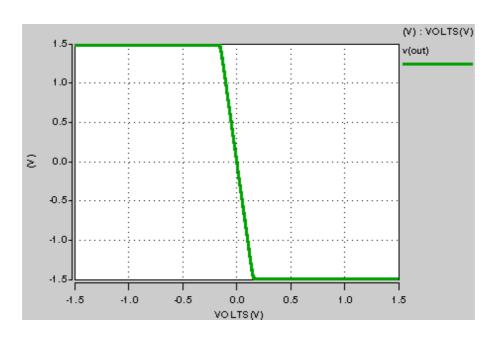

## シミュレーション

## 入力電圧範囲 (評価回路a: DC)

入力電圧を掃引し、 出力電圧が飽和し 始める入力電圧の値

最大値 148.58 [mV] 最小値 -148.93 [mV]

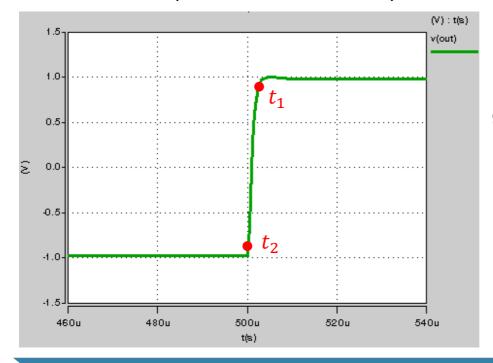

#### シミュレーション

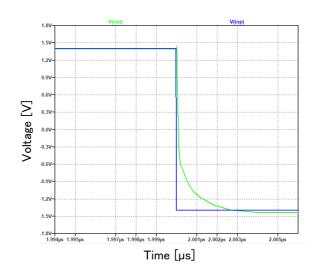

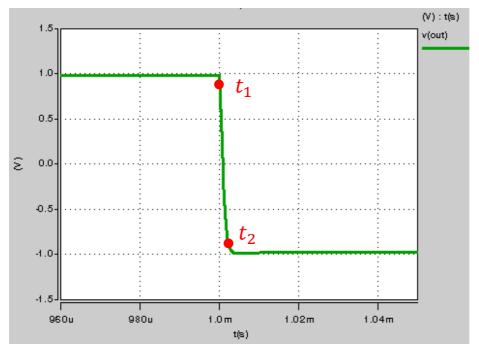

#### スルーレート (評価回路a: TRAN)

出力電圧が -900mV 900mVになった時刻

評価式

$$SR = \frac{1.8}{t_2 - t_1}$$

立ち上がり 0.74 [V/µS]

Copyright © 2020 ICLab. All Rights Reserved.

8 /11

## シミュレーション

#### スルーレート (評価回路a: TRAN)

出力電圧が -900mV 900mVになった時刻

評価式

$$SR = \frac{1.8}{t_2 - t_1}$$

立ち下がり 0.80 [V/µS]

| 項目   | 評価結果       | 単位 |

|------|------------|----|

| 消費電流 | 1.2837e-05 | A  |

| 項目     |       | 評価結果    | 単位   |

|--------|-------|---------|------|

| 直流利    | 得     | 53.7365 | dB   |

| 位相余    | :裕    | 63.3172 | deg  |

| 帯域幅    |       | 93.7    | kHz  |

| 入力電圧範囲 | 最大値   | 148.58  | mV   |

|        | 最小値   | -148.93 | mV   |

| スルーレート | 立ち上がり | 0.74    | V/µS |

|        | 立ち下がり | 0.80    | V/µS |

Copyright © 2020 ICLab. All Rights Reserved.

10 /11

#### まとめ

- ・構成やパラメータ調整による特性の変化 について知ることが出来た

- ・3部門で入賞することが出来たのでよかった

- ・MOSFETなどのばらつきや特性変動に気を 付け設計を行う

このような貴重な機会を与えてくださった コンテスト運営及び審査委員の皆様と 協賛企業の皆様に深く感謝を申し上げます

## 演算増幅器設計コンテスト 第3部門 2位

愛知工業大学 工学研究科 電気電子工学専攻 光量子デバイス研究室 修士1年 日比 彪斗

方針 回路 sim 結果 考察 まとめ

#### 部門3の評価式

得点 =  $\frac{$ 電源電圧変動除去比[倍] × 同相除去比[倍]  $}{$ 直流利得[倍]<sup>2</sup> × 電源電圧[V]

dBではなく真値で計算

電源電圧変動除去比

の二つに注目して回路構成を考える

同相除去比

## 設計方針

- 電源電圧変動除去比(PSRR)

- →バイアス段にて依存性をなくす

- 同相除去比(CMRR)

- →ダイオード接続差動段+差動増幅 にて同相利得→減,差動利得→増

方針 回路 sim 結果 考察 まとめ

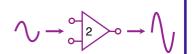

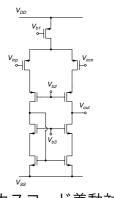

## 提出回路

m1 W=4.0u L=0.8u m2 W=4.0u L=0.8u M=5 m3 W=1.5u L=0.8u m4 W=1.5u L=0.8u R1 15k m5 W=8.4u L=0.8u m6 W=8.4u L=0.8u m7 W=2u L=0.8u m8 W=2u L=0.8u m9 W=3.2u L=0.8u m10 W=6.8u L=0.8u m11 W=6.8u L=0.8u m12 W=1.6u L=0.8u m13 W=1.6u L=0.8u m14 W=3.0u L=0.8u m15 W=9.2u L=0.8u m16 W=2.2u L=0.8u C1 10p R2 30k

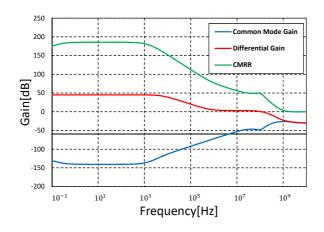

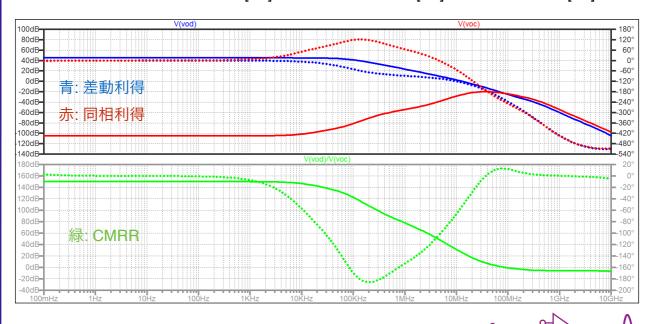

## 同相除去比(CMRR)

同相利得 Acom = -140.59dB 差動利得 Adif=45.05dB

CMRR=185.71dB

同相除去比

方針 回路 sim 結果 考察 まとめ

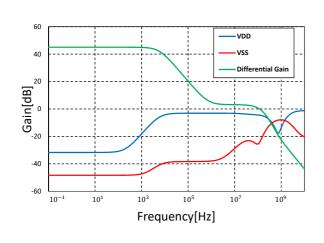

## 電源電圧変動除去比(PSRR)

VDD変動利得

Avdd = -31.687dB

VSS変動利得

Avss=-48.314dB

差動利得

Adif=45.054dB

PSRR(VDD)=76.741dB

PSRR(VSS)=93.368dB

## 直流利得

#### 直流利得

Simulation値:4.5056e+01dB 実際 : 7.5425e+01dB

#### 出力抵抗

Simulation値:2.1447e+02 $\Omega$  実際 :6.4273e+05 $\Omega$

方針 回路 sim 結果 考察 まとめ

## 評価結果

| 項目        | 評価結果(今年度)  |

|-----------|------------|

| 電源電圧変動除去比 | 7.6741e+01 |

| 同相除去比     | 1.8571e+02 |

| 直流利得      | 7.5460e+01 |

| 電源電圧      | 3.0000e+00 |

| スコア       | 1.2573e+05 |

## 考察

- 同相除去比が大きく伸びた

- →差動段にて同相利得を大きく落とすことが出来た

- 直流利得が高くなってしまった

- →出力抵抗がかなり大きく設計されたため

- ⇒出力抵抗を下げ、直流利得>電源電圧変動除去比で 設計したらもっとスコアが伸びたと考える

方針 回路 sim 結果 考察 まとめ

## 感想

今回、回路設計にて上位入賞することができ嬉しく思います。

しかし、まだまだ回路設計への知識が足りないと感じる部分が多々あり、素子値が決定できない回路も多くありました。

来年度の目標として、課題を残さない納得のできる回路を作成します。

貴重な機会を設けて下さいました 運営の皆様及び協賛企業の皆様に深く感謝を申し上げます

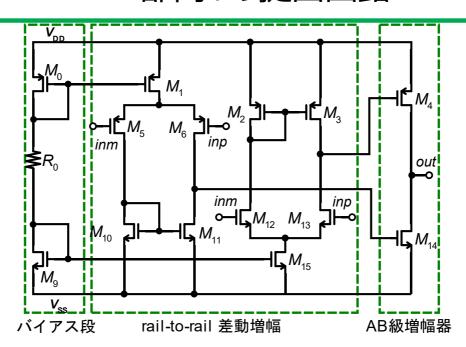

# 演算増幅器設計コンテスト シミュレーションの部

部門1:1位

2020年12月3日 東京理科大学 理工学研究科 電気工学専攻 兵庫研究室 齋藤滉牛

Tokyo University of Science HYOGO Lab.

## 部門1の評価項目

• 評価式

スルーレート[V/s] × 同相入力範囲[%] × 直流利得[dB] 消費電流[A]

- 設計方針

- ◆ スルーレートと消費電流のトレードオフを 緩和する回路を設計

- ◆ AB級増幅器を出力段に用いることで低消費電流

- ◆ rail-to-railでAB級を動作させる

- →レベルシフトを用いないことで無信号時低電流

#### スルーレート

$\omega_0$ が3dB帯域幅、

Aoが閉ループ利得

とすると時定数

は以下のようになる

$$\tau = \frac{1}{\left(1 + \frac{R_2}{(R_1 + R_2)}A_0\right)\omega_0}$$

$A_0$ または、 $\omega_0$ が大きければ時定数が小さくなる

Tokyo University of Science **HYOGO Lab**.

2

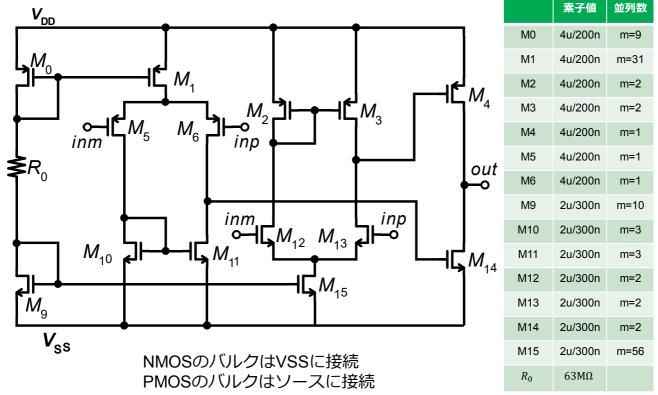

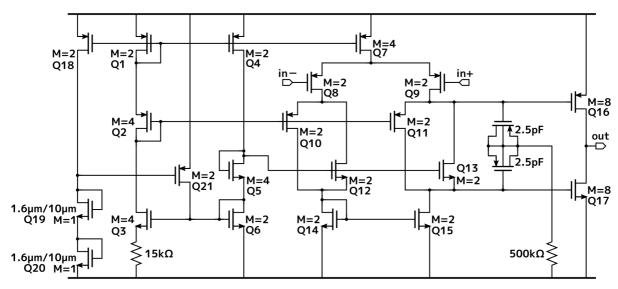

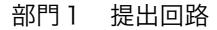

## 部門1の提出回路

消費電流を小さくしても十分な出力抵抗を確保できる。

## 部門1の提出回路(素子値)

Tokyo University of Science **HYOGO Lab**.

4

## 消費電流

|              | VDD×0.9 | VDD           | VDD×1.1 |

|--------------|---------|---------------|---------|

| <b>−40°C</b> | 518 nA  | 618 nA        | 727 nA  |

| 25°C         | 540 nA  | <u>634 nA</u> | 734 nA  |

| 80°C         | 563 nA  | 654 nA        | 750 nA  |

- 電源電圧を±10%変動

- ・温度を-40℃, 25℃, 80℃に変動

- 基準 (VDD, 25℃) における値を無信号時の 消費電流として評価

#### 全ての条件で要件(基準の±50%以内)を満たしている

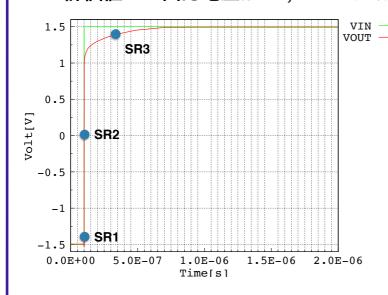

## スルーレート(立ち下がり)

- スルーレートは SR₁〜SR₃における 傾きの平均値で評価 (立ち上りも同様)

- 評価式  $SR = \frac{SR_1 + SR_2 + SR_3}{3}$

| SR <sub>1</sub> [V/s]  | SR <sub>2</sub> [V/s]  | SR <sub>3</sub> [V/s]  | SR [V/s]               |

|------------------------|------------------------|------------------------|------------------------|

| $-5.19 \times 10^{10}$ | $-1.49 \times 10^{10}$ | $-0.49 \times 10^{10}$ | $-2.39 \times 10^{10}$ |

Tokyo University of Science **HYOGO Lab**.

6

## スルーレート(立ち上がり)

- SR(立ち下り) -2.39×10<sup>10</sup> V/s

- SR(立ち上り) <u>2.34×10<sup>10</sup> V/s</u>

| SR <sub>1</sub> [V/s] | SR <sub>2</sub> [V/s] | SR <sub>3</sub> [V/s] | SR [V/s]            |

|-----------------------|-----------------------|-----------------------|---------------------|

| $5.51\times10^{10}$   | $1.35\times10^{10}$   | $0.16\times10^{10}$   | $2.34\times10^{10}$ |

## 直流利得(補正前)

• 直流利得(@0.1 Hz) (補正前)

$$A_{sim} = 10.9 \text{ dB}$$

出力抵抗

$$r_{sim} = 7.24 \text{ k}\Omega$$

$$\theta = 100 \deg$$

$$f = 1 \text{ MHz}$$

Tokyo University of Science **HYOGO Lab**.

8

## 直流利得(補正後)

DC gain and output resistance corrector

Output resistance :  $1.9666e+07 \Omega$

Simulation results: 直流利得(補正後) dB DC gain 10.929 補正前  $A = 70.8 \, dB$ Output resistance 7240 Ω Calculate 出力抵抗(補正後) Corrected values:  $r = 19.7 \,\mathrm{M}\Omega$ DC gain : 7.0792e+01 dB 補正後

## 結果

| 項目     | 評価結果       | 単位  |

|--------|------------|-----|

| スルーレート | 2.5344e+10 | V/s |

| 消費電流   | 6.1018e-07 | Α   |

| 同相入力範囲 | 1.0000e+02 | %   |

| 直流利得   | 7.0185e+01 | dB  |

| スコア    | 2.9152e+20 |     |

- ・消費電流を抑えた

- 高スルーレートを実現できた

Tokyo University of Science **HYOGO Lab**.

10

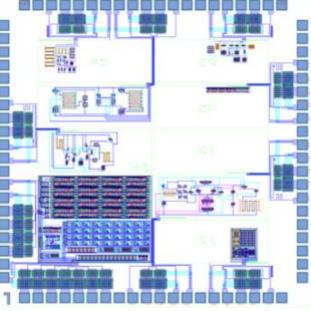

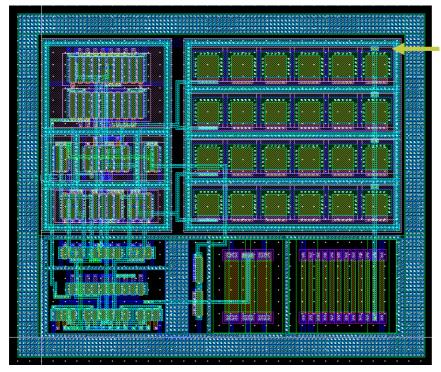

## OPamp実装

今年試作の部は中止となってしまいましたが、 兵庫研究室では独自に試作をしました。

# Since 1881

## まとめ

#### 感想

- ・部門1で1位を取ることができて良かった

- ・部門2,3にまで手が回らなかったので来年頑張りたい

#### 謝辞

このような機会を与えてくださった演算増幅器設計 コンテスト運営の方々および協賛企業の方々に厚く 御礼申し上げます。

本コンテストは東京大学大規模集積システム設計教育研究センターを通し,シノプシス株式会社、日本ケイデンス株式会社の協力で行われたものである。

# 演算増幅器設計コンテスト

部門2:5位 部門3:5位 部門4:1位

2020/12/3

# 東京理科大学 理工学研究科 楳田研究室 川原啓輔

Department of Electrical Engineering, Faculty of Science and Technology, Tokyo University of Science

Tokyo University of Science, Umeda Laboratory

## はじめに

- ■今年度は感染症の影響により試作の部が中止

- ■東京理科大学兵庫研究室ではコンテストとは別に 演算増幅器のシャトル試作を実施

- ■試作回路に定数調整を加えた回路を部門4に提出

## 概要

- ■試作回路

- ■評価項目と要件

- ■回路構成とレイアウト

- ■測定系と測定結果

- ■部門 4

- ■評価項目と要件

- ■回路構成

- ■シミュレーション結果

- ■まとめ

Tokyo University of Science, Umeda Laboratory

3

# 試作回路 - 評価項目と要件

表1:要件

| 項目        | 要件                    | 備考                                   |

|-----------|-----------------------|--------------------------------------|

| 電源電圧      | 3V                    | 固定                                   |

| 直流利得      | 40dB 以上               | ⊠ 1(b)                               |

| 位相余裕      | 45 度以上                | 図 1(b),負荷容量 ±10%変動                   |

| 帯域幅       | 20kHz 以上              | ⊠ 1(a)                               |

| 出力オフセット電圧 | ±100mV 以内             | ⊠ 1(a)                               |

| 入力電圧範囲    | ±100mV 以上             | ⊠ 1(a)                               |

| スルーレート    | ±1V/μs 以上             | ⊠ 1(a)                               |

| 全高調波歪     | 0.1%以下                | 入力:1kHz, 振幅 1mV, DC オフセット 0V, 図 1(a) |

| 占有面積      | 0.2mm <sup>2</sup> 以内 |                                      |

- ■昨年度の試作の部の評価回路に準拠

- ■評価項目:無信号時の消費電流

引用: https://www.ec.ict.e.titech.ac.jp/opamp/2018/design.pdf

## 試作回路 - 設計方針

| 121・女団    |                       |                                      |  |

|-----------|-----------------------|--------------------------------------|--|

| 項目        | 要件                    | 備考                                   |  |

| 電源電圧      | 3V                    | 固定                                   |  |

| 直流利得      | 40個以上                 | 図 1(b)                               |  |

| 位相余裕      | 45 度以上                | 図 1(b), 負荷容量 ±10%変動                  |  |

| 帯域幅       | 20kHz以上               | ⊠ 1(a)                               |  |

| 出力オフセット電圧 | ±100mV 以内             | ⊠ 1(a)                               |  |

| 入力電圧範囲    | ±100mV 以上             | 図 1(a)                               |  |

| スルーレート    | ±1V/μs以上              | 図 1(a)                               |  |

| 全高調波歪     | 0.1%以下                | 入力:1kHz, 振幅 1mV, DC オフセット 0V, 図 1(a) |  |

| 占有面積      | 0.2mm <sup>2</sup> 以内 |                                      |  |

表1: 亜

- ■負荷が重く、高スルーレートと低消費電力の両立が課題 →AB級出力段を採用

- ■AB級はバラツキの影響を受けやすいため注意して設計

Tokyo University of Science, Umeda Laboratory

5

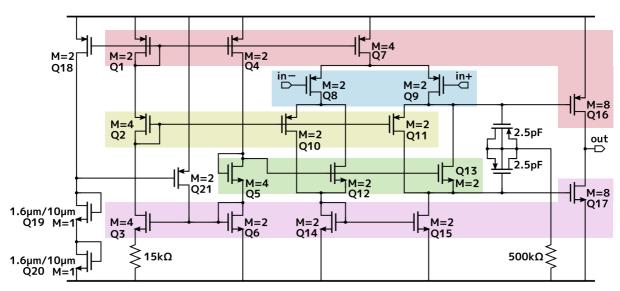

## 試作回路 – 構成

※バックゲートは電源に接続(キャパシタを除く)

# 試作回路 - 素子定数

表記のないNMOS: $\frac{W}{L} = \frac{4\mu \text{m}}{1.6\mu \text{m}}$ , PMOS: $\frac{W}{L} = \frac{10\mu \text{m}}{1.6\mu \text{m}}$

■MOSの並列数Mを偶数に設定→コモンセントロイド配置

Tokyo University of Science, Umeda Laboratory

7

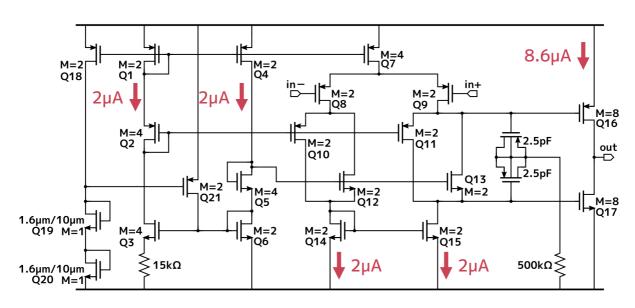

# 試作回路 - バイアス値

- ■出力段に電流を配分→スルーレート向上

- ■バラツキを考慮して電流比を約4倍に設定

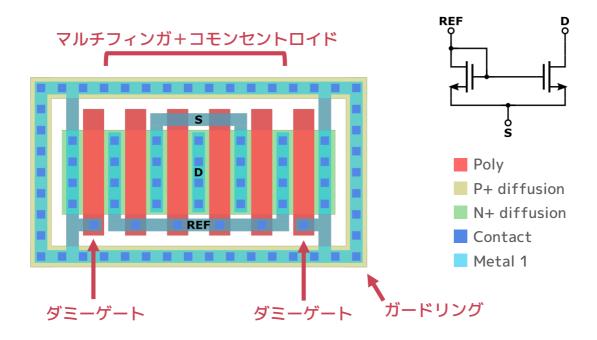

## レイアウト手順

- 1. マッチング対ごとにセルを作成し配線(Metal1)

- 2. 各セルを接続 (Metal2)

- 3. グローバル配線 (Metal3)

Tokyo University of Science, Umeda Laboratory

9

## 差動対のレイアウト

# カレントミラーのレイアウト

※Isolation領域等は省略

Tokyo University of Science, Umeda Laboratory

11

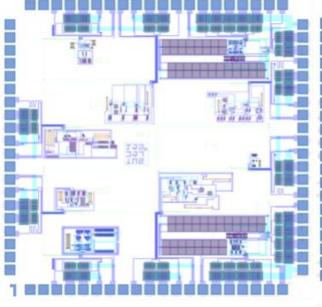

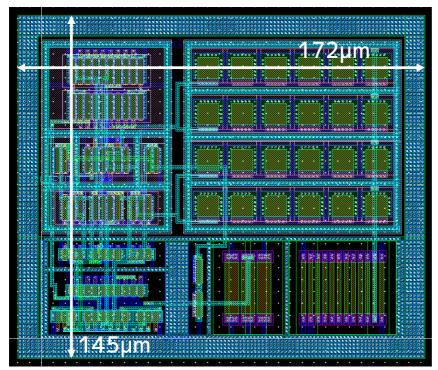

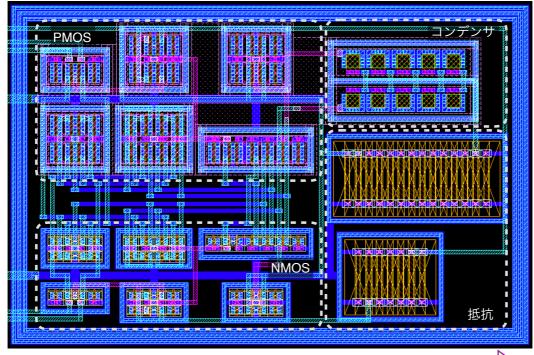

# 全体レイアウト

チップ写真

(**占有面**積) = 0.025mm<sup>2</sup>

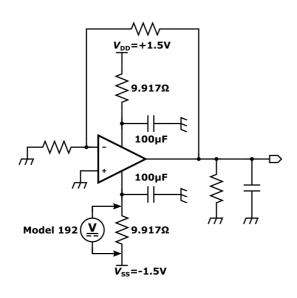

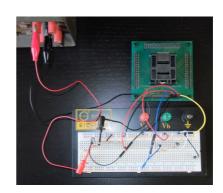

# 消費電流測定系

- ■シャント抵抗を挿入し電流を検出

- ■シャント抵抗の四端子法による実測値は9.917Ω

Tokyo University of Science, Umeda Laboratory

13

# 消費電流測定結果

|                          | Sim.                                      | Meas.<br>(CHIP1) | Meas.<br>(CHIP2) | Meas.<br>(CHIP3) | Meas.<br>(平均) |

|--------------------------|-------------------------------------------|------------------|------------------|------------------|---------------|

| VDD側<br>消費電流 (µA)        | 19.4 (Fast)<br>18.3 (Typ.)<br>17.1 (Slow) | 23.6             | 20.1             | 16.1             | 19.9          |

| VSS側<br>消費電流 (µA)        | 19.3 (Fast)<br>18.2 (Typ.)<br>17.0 (Slow) | 40.7             | 27.0             | 23.4             | 30.4          |

| VDD側とVSS側の<br>平均消費電流(µA) | 19.4 (Fast)<br>18.3 (Typ.)<br>17.1 (Slow) | 32.2             | 23.5             | 19.8             | 25.2          |

- VDD側消費電流はシミュレーションと概ね一致

- VSS側消費電流はシミュレーションに対して増加 (出力オフセットの影響)

- ■最も消費電流の少ないCHIP3を詳細に測定

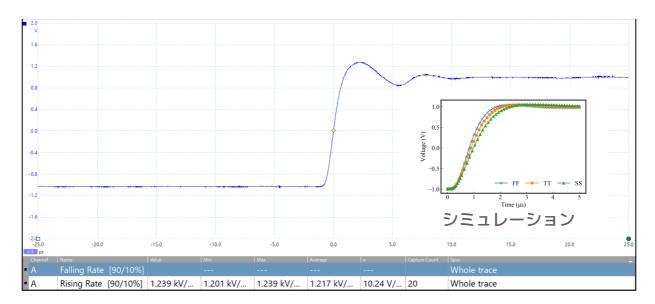

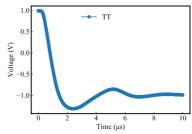

# **CHIP3 - 上昇ステップ応答**

- ■上昇スルーレート=1.2V/µs

- ■シミュレーションに対してリンギング増加

Tokyo University of Science, Umeda Laboratory

15

# **CHIP3 - 下降ステップ応答**

- 下降スルーレート=1.3V/µs

- ■シミュレーションに対してリンギング増加

# リンギング増の原因

蓄積層を使用するための B端子への接続を忘れた◎ LVS検出されないため注意

バックゲート開放時 のシミュレーション結果

Tokyo University of Science, Umeda Laboratory

17

# 測定結果まとめ

| 項目        | Sim. (Typ.)                                   | Meas. (CHIP3)                              |

|-----------|-----------------------------------------------|--------------------------------------------|

| 入力電圧範囲    | ±140 mV                                       | ±150 mV                                    |

| -3dB帯域幅   | 70 kHz                                        | 100 kHz以上                                  |

| 出力オフセット電圧 | 0.23 mV                                       | −39 mV                                     |

| 全高調波歪み率   | 0.045%<br>(@20 mV <sub>PP</sub> output swing) | 0.80%<br>(@2 V <sub>PP</sub> output swing) |

| 上昇スルーレート  | 1.3 V/µs                                      | 1.2 V/μs                                   |

| 下降スルーレート  | 1.4 V/µs                                      | 1.3 V/µs                                   |

| 消費電流      | 18.2 μΑ                                       | 19.8 μΑ                                    |

- ■概ねシミュレーション結果と測定結果が一致

- ■出力オフセットが増加→差動対のバイアス値に差?

# 部門4 - 評価項目と要件

試作回路の10倍

表1:要件

| 項目        | 要件                    | 備考                                   |

|-----------|-----------------------|--------------------------------------|

| 電源電圧      | 3V                    | 固定                                   |

| 直流利得      | 40dB 以上               | <b>図</b> 1(b)                        |

| 位相余裕      | 45 度以上                | 図 1(b), 負荷容量 ±10%変動                  |

| 帯域幅       | 20kHz 以上              | 図 1(a)                               |

| 出力オフセット電圧 | ±100mV 以内             | 図 1(a)                               |

| 入力電圧範囲    | ±100mV 以上             | 図 1(a)                               |

| スルーレート    | ±1V/μs以上              | ☑ 1(a)                               |

| 全高調波歪     | 0.1%以下                | 入力:1kHz, 振幅 1mV, DC オフセット 0V, 図 1(a) |

| 占有面積      | 0.2mm <sup>2</sup> 以内 |                                      |

- ■負荷抵抗値・帰還抵抗値が試作回路の10倍

- ■評価項目:無信号時の消費電流

引用: https://www.ec.ict.e.titech.ac.jp/opamp/2020/design2020.pdf

Tokyo University of Science, Umeda Laboratory

19

# 部門4-提出回路

**NMOS**:  $\frac{W}{L} = \frac{10 \, \mu \text{m}}{1.8 \, \mu \text{m}}$ , **PMOS**:  $\frac{W}{L} = \frac{30 \, \mu \text{m}}{1.8 \, \mu \text{m}}$

■ 試作回路から定数調整・スタートアップ回路を削除

# 部門4-結果

| 項目        | シミュレーション結果(Typ.)                              |  |

|-----------|-----------------------------------------------|--|

| 入力電圧範囲    | ±150 mV                                       |  |

| -3dB帯域幅   | 30 kHz                                        |  |

| 出力オフセット電圧 | 0.13 mV                                       |  |

| 全高調波歪み率   | 0.016%<br>(@20 mV <sub>PP</sub> output swing) |  |

| 上昇スルーレート  | 0.98 V/μs <sup>*</sup>                        |  |

| 下降スルーレート  | 0.94 V/μs <sup>*</sup>                        |  |

| 項目   | 評価結果       | 単位 |

|------|------------|----|

| 消費電流 | 4.1303e-06 | Α  |

※手元のシミュレーション結果、コンテストのシステムとは評価手法が若干異なる

Tokyo University of Science, Umeda Laboratory

21

# まとめ

- ■回路の構成とレイアウト上の工夫点を紹介

- ■測定結果とシミュレーション結果が概ね一致

- ■試作回路はステップ応答のリンギングとオフセットが増加

- ■演算増幅器の基本的な設計フローを理解できたのでより確実で高度な設計を模索したい

### 謝辞

演算増幅器設計コンテスト協賛企業の皆様と運営の皆様、 またチップ試作の機会を設けていただいた東京理科大学兵庫研究室に 心より感謝を申し上げます。

# 演算増幅器設計コンテスト

部門1 5位 部門2 1位 部門3 3位

> 群馬大学 修士 2 年 猿田将大 2020 / 12 /03

### 設計方針

評価式

設計方針

評価値 = スルーレート[V/s] \* 同相入力範囲 [%] \* 直流利得 [dB] 消費電流 [A]

部門1はスルーレートと消費電流で差がつく(重要!!)

- □ 高スルーレート・低消費電流

- Rail to Rail 回路

- □ 同相入力範囲を 100% に

カスコードを使用しない

0 2 0

Vdd = 1.5 Vss = -1.5 バルク pmos : Vdd noms : Vss

$\rightarrow$

### 直流利得

### AC 解析

### ・直流利得の補正計算

直流利得(シミュレーション値) A<sub>0sim</sub> = 21.7397 dB

出力抵抗(シミュレーション値)

$r_0 = 2725.963 \Omega$

負荷抵抗

$RL = 20 k\Omega$

### 直流利得補正式

$$A_0 = A_{0_{sim}} \frac{R_L + r_0}{R_L}$$

### 直流利得補正後

$A_0 = 51.889 dB$

### スルーレート 立ち上がり

### <u>過渡解析</u>

評価値: 出力電圧が 0V, ±90% における傾き 3点の平均値

SR1 = 4.87e + 9

SR2 = 3.65e + 9

SR3 = 7.98e + 5

SRR = 2.84e + 9

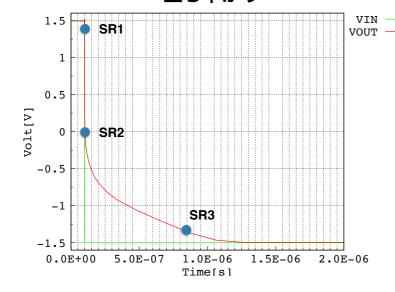

### スルーレート

## 過渡解析 立ち下がり

SR1 = -7.58e + 9

SR2 = -1.12e + 8

SR3 = -7.65e + 5

SRF = -2.56e + 9

立ち上がり: 2.84e+9 V/s 立ち下がり: 2.56e+9 V/s

### 部門 1 提出回路結果

|              | 昨年度        | 今年度        |   |

|--------------|------------|------------|---|

| スルーレート [V/s] | 2.1288E+10 | 3.3546E+09 | + |

| 消費電流 [uA]    | 1.0611     | 1.6424     | + |

| 同相入力範囲 [%]   | 100        | 100        |   |

| 直流利得 [dB]    | 79.285     | 51.869     | + |

| スコア          | 1.5906E+20 | 1.0594E+19 | + |

### 部門2 設計方針

### 評価式

評価値 = — 利得帯域幅積 × 位相余裕

消費電力<sup>2</sup>× 出力抵抗×入力換算雑音

### 設計方針

- □消費電力

- → 2乗が効いてくるので低電圧に

- □ 出力抵抗

- □ 入力換算雑音

- **→** PMOS 入力で設計

### 設計方針

(続き)

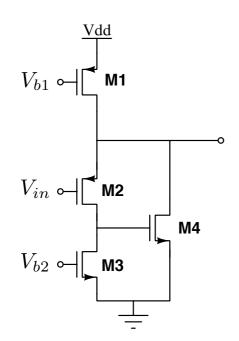

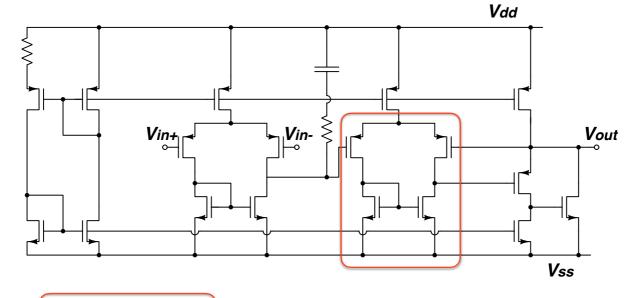

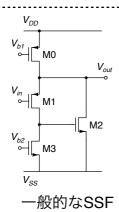

□ 出力抵抗 ① スーパーソースフォロア

$$Z_{out} \simeq \frac{1}{g_{m2}g_{m4}r_{o2}}$$

出力抵抗低減

(続き)

□ 出力抵抗

### ② 負帰還回路

$$Z_{out} = \frac{r_{o,A3}}{1 + A_2}$$

### 負帰還アンプの利得分 さらに出力抵抗を低減

設計方針

(続き)

### □ 入力換算雑音

熱雑音

$$5k_B T_{\gamma} \frac{1}{g_{m2,3}} \left(1 + \frac{g_{m4,5}}{g_{m2,3}}\right) \Delta f$$

M2, M3 の LW 比を大きく M4, M5 の LW 比を小さく

フリッカ雑音

$$\frac{2k_p}{C_{ox}W_{2,3}L_{2,3}}\left(1 + \frac{K_n\mu_nL_{2,3}^2}{K_p\mu_pL_{4,5}^2}\right)\frac{\Delta f}{f}$$

M2, M3 の面積を大きく M4, M5 の L を小さく

$k_B$ :ボルツマン係数  $K_{n,p}$ :フリッカ雑音係数

$\gamma$  : チャネル熱雑音係数

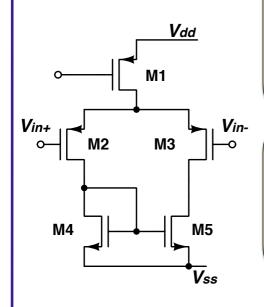

### 案1 回路スコア

|             | 案 1 回路特性値 |

|-------------|-----------|

| 消費電力 [W]    | 3.45E-05  |

| 出力抵抗 [Ω]    | 3.93E-01  |

| 入力換算雑音 [V]  | 2.51E-03  |

| 利得帯域幅積 [Hz] | 6.99E+06  |

| 位相余裕 [deg]  | 7.53E+01  |

| スコア         | 4.46E+20  |

### 案1回路 修正方針

### 出力抵抗をさらに低減させたい

$$Z_{out} = \frac{r_{o,A3}}{1 + A_2}$$

### 負帰還アンプをカスコードに変更

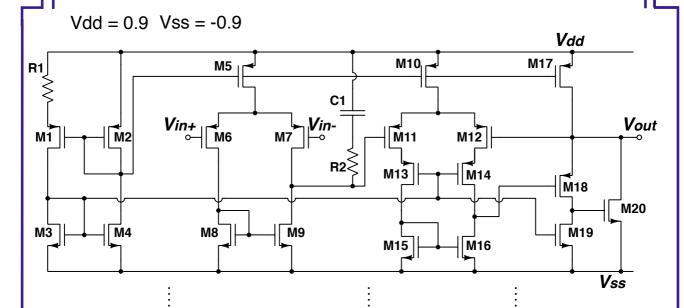

### 最終提出回路

R1: 3k

M1, M2: L=0.8u W=1.3u

M3, M4: L=12u W=16u

M5: L=0.8u W=1.5u

M6, M7: L=1.5u W=15u

M8, M9: L=5.6u W=0.56u

R2: 10.4k

C1: 0.6p

M10: L=0.8u W=0.4u

M11, M12: L=0.8u W=8.0u

M13, M14: L=0.3u W=3.0u

M15, M16: L=4.2u W=0.42u

M17: L=0.8u W=6.7u M18: L=1.0u W=26.5u

M19: L=12u W=3.0u

M20: L=0.18u W=10u

### 消費電力

### 消費電流

|    |       | 電源電圧     |          |          |  |

|----|-------|----------|----------|----------|--|

|    |       | vdd×0.9  | Vdd      | vdd×1.1  |  |

|    | -40°C | 16.70 uA | 21.72 uA | 27.09 uA |  |

| 温度 | 25°C  | 14.76 uA | 19.23 uA | 24.08 uA |  |

|    | 80°C  | 13.40 uA | 17.45 uA | 21.87 uA |  |

要件:申告した電源電圧と温度25°Cの時の消費電流の50% 以内 9.62 uW(50%) ~ 28.85 uW(150%)

### 消費電力

評価値: 消費電力 = 申告された電源電圧 × 消費電流

$1.8 \times 19.23 uA = 34.61 uW < 100 mW$

### 位相余裕・利得帯域幅積

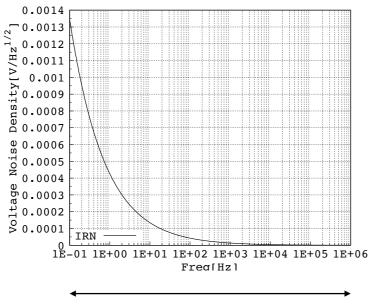

### 入力換算雑音

### NOISE 解析

### ・入力換算雑音

1.70 mV

積分值

### 部門2 最終提出回路スコア

|             | 案 1 回路特性値 | 最終提出回路特性値  |

|-------------|-----------|------------|

| 消費電力 [W]    | 3.45E-05  | 3.4664E-05 |

| 出力抵抗 [Ω]    | 3.93E-01  | 1.0018E-01 |

| 入力換算雑音 [V]  | 2.51E-03  | 1.7429E-03 |

| 利得帯域幅積 [Hz] | 6.99E+06  | 5.9053E+06 |

| 位相余裕 [deg]  | 7.53E+01  | 5.3555E+01 |

| スコア         | 4.46E+20  | 1.5074E+21 |

出力抵抗を 0.1Ω に近づけることができた 利得帯域幅積に着目しなかったことがスコアが伸びなかった原因

### 部門3 設計方針

評価式

### 設計方針

- □ 直流利得

- **──→** 真値の2乗が効いてくるので 40dB を目指す

- → 部門2の回路を使いまわせる

- □ PSRR

M3, M4: L=13.4u W=16.4u

M8, M9: L=4.2u W=0.42u

R2: 20k

C1: 1.0p

→ 利得と連動しているので気にしない

M19: L=13.4u W=3.0u

M20: L=0.18u W=10u

M15, M16: L=4.2u W=0.42u

### 直流利得

・直流利得の補正計算

直流利得(シミュレーション値)

A0sim = 41.5825 dB

出力抵抗 (シミュレーション値)

$r_0 = 6.7058 \text{ m}\Omega$

負荷抵抗

$RL = 20 k\Omega$

### 直流利得補正式

$$A_0 = A_{0_{sim}} \frac{R_L + r_0}{R_L}$$

直流利得補正後

$A_0 = 41.538 dB$

### **CMRR**

CMRR: 93.612 dB

同相利得: -52.029 dB

差動利得: 41.582 dB

### **PSRR**

黒: PSRR(VDD側) 青: PSRR(VSS側)

54.1581 dB 43.9389 dB

### 部門3 提出回路の結果

|                | 回路特性値      |

|----------------|------------|

| 電源電圧変動除去比 [dB] | 43.941     |

| 同相除去比 [dB]     | 132.44     |

| 直流利得 [dB]      | 41.538     |

| 電源電圧 [V]       | 1.8        |

| スコア            | 2.5703E+04 |

直流利得を40dBに近づけることができた CMRR を上げる手立てを考えるべきだった

### 感想

- 今まで部門 1 をメインに参加してきたが、今年は他の部門にも 積極的に参加した

- どの特性をメインに設計を行っていくかで設計方法が変わるので、 今年初めて部門2、3に参加して、新しい気づきや知識、難しさを 得たので、後輩に4年生から全ての部門への参加を促していきたい

- 最後に ] 位を取れて良かった

### -謝辞·

演算増幅器設計コンテスト運営の皆様 協賛企業の皆様 厚く感謝申し上げます

# 演算増幅器設計コンテスト

部門2: 2位 部門3: 1位 部門4: 奨励賞

2020年12月3日

群馬大学 理工学府 理工学専攻 電子情報・数理教育プログラム 修士1年 齋藤彰寛

### **OUTLINE**

### 設計方針

・評価式で見る部門2

部門2の得点評価式は以下のようになっている。

また、それぞれの特性について一般的な設計をした場合の範囲は以下の表となる。

|                       | 最小                   | 最大                   | 最大/最小   |

|-----------------------|----------------------|----------------------|---------|

| 利得帯域幅積 [Hz]           | 1E+06                | 1E+09                | 1.0E+03 |

| 位相余裕 [°]              | 45                   | 100                  | 2.2E+00 |

| 消費電力 <sup>2</sup> [W] | (1E-05) <sup>2</sup> | (1E-03) <sup>2</sup> | 1.0E+04 |

| 出力抵抗 [Ω]              | 0.1                  | 1E+05                | 1.0E+06 |

| 入力換算雑音 [V/√Hz]        | 1E-03                | 1E-01                | 1.0E+02 |

GUNMA UNIVERSITY TAKAI-LAB  $\longrightarrow \bigcirc$  4  $\longrightarrow \bigcirc$  4

・評価式で見る部門2

### 得点への影響

大 出力抵抗→消費電力→利得帯域幅積→入力換算雑音→位相余裕 小

高得点を取るためには基本的にはこの優先度で設計を行うことが重要。

|                       | 最小                   | 最大                   | 最大/最小   |       |

|-----------------------|----------------------|----------------------|---------|-------|

| 利得帯域幅積 [Hz]           | 1E+06                | 1E+09                | 1.0E+03 | 3 < > |

| 位相余裕 [°]              | 45                   | 100                  | 2.2E+00 | 5 _   |

| 消費電力 <sup>2</sup> [W] | (1E-05) <sup>2</sup> | (1E-03) <sup>2</sup> | 1.0E+04 | 2 ,   |

| 出力抵抗 [Ω]              | 0.1                  | 1E+05                | 1.0E+06 | 1 7   |

| 入力換算雑音 [V/√Hz]        | 1E-03                | 1E-01                | 1.0E+02 | 4     |

GUNMA UNIVERSITY TAKAI-LAB  $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0$

### 設計方針

- ・部門2の回路設計方針

- 1. 出力抵抗を最小の0.1Ωにする。

- →負帰還アンプ + スーパーソースフォロワ

- 2. 消費電力を小さくする。

- →1段増幅。ゲインブースト回路付き差動対を使用

- 3. 利得帯域幅積を大きくする。

- →差動対をカスコード化 + 小型MOS

スーパーソースフォロワ (SSF) の出力抵抗の計算式は以下のようになる。

$$r_{out} = \frac{1}{\frac{1}{r_{o2}} + g_{m2} + g_{m1}g_{m2}r_{o1}} \approx \frac{1}{g_{m1}g_{m2}r_{o1}}$$

https://www.researchgate.net/publication/ 321034471 Design and Analysis of Super Source Follower

利得は約1倍なので、出力段にバッファとして用いることができる。

GUNMA UNIVERSITY TAKAI-LAB

- ・部門2の回路設計方針

- 1. 出力抵抗を最小の0.1Ωにする。

- →負帰還アンプ + スーパーソースフォロワ

- 2. 消費電力を小さくする。

- →1段増幅。ゲインブースト回路付き差動対を使用

- 3. 利得帯域幅積を大きくする。

- →差動対をカスコード化 + 小型MOS

負帰還アンプ付きSSF 負帰還アンプとSSFを組み合わせた場合、出力抵抗は以下のようになる。

$$r_{out} \approx \frac{1}{Ag_{m1}g_{m2}r_{o1}}$$

→SSFのみに比べ、更に出力抵抗の低減が可能 (ただしアンプ1つ分消費電力が増加する)

GUNMA UNIVERSITY TAKAI-LAB  $\longrightarrow 0$  7  $\longrightarrow$  7

### 設計方針

- ・部門2の回路設計方針

- 1. 出力抵抗を最小の0.1Ωにする。

- →負帰還アンプ + スーパーソースフォロワ

- 2. 消費電力を小さくする。

- →1段増幅。ゲインブースト回路付き差動対を使用

- 3. 利得帯域幅積を大きくする。

- →差動対をカスコード化 + 小型MOS

ゲインブースト回路付き差動対

低消費電流 + 後述の小型MOS だと利得が稼ぎづらい。 ゲインブースト回路を用いて1段で40dB以上増幅できる ように。

GUNMA UNIVERSITY TAKAI-LAB  $\longrightarrow$  8  $\longrightarrow$  8  $\longrightarrow$  0

- ・部門2の回路設計方針

- 1. 出力抵抗を最小の0.1Ωにする。

- →負帰還アンプ+スーパーソースフォロワ

- 2. 消費電力を小さくする。

- →1段増幅。ゲインブースト回路付き差動対を使用

- 3. 利得帯域幅積を大きくする。

- →差動対をカスコード化 + 小型MOS

カスコード差動対

周波数特性が悪化する主な原因

- →MOSの寄生容量

- ・差動対をカスコード化し、ミラー容量を低減。

- ・チャネル長Lの小さいMOSで設計する。

GUNMA UNIVERSITY TAKAI-LAB  $0 \rightarrow 9 \rightarrow 0$

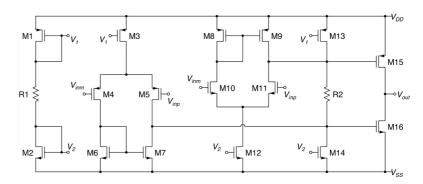

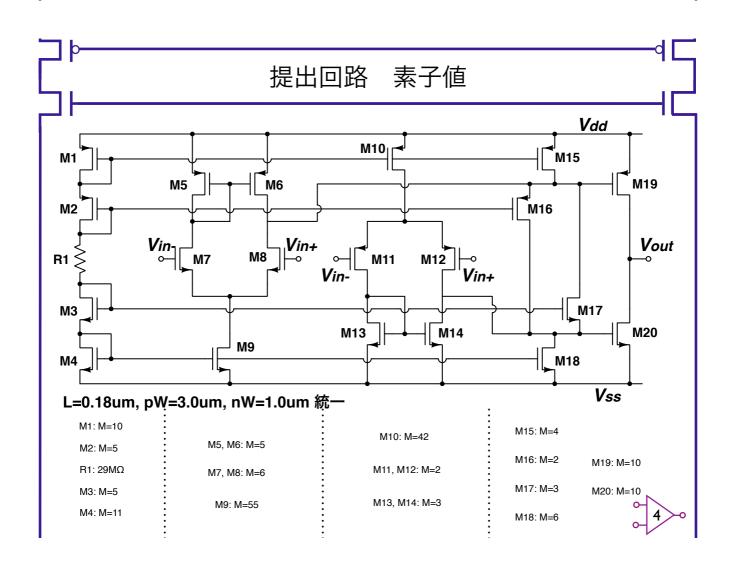

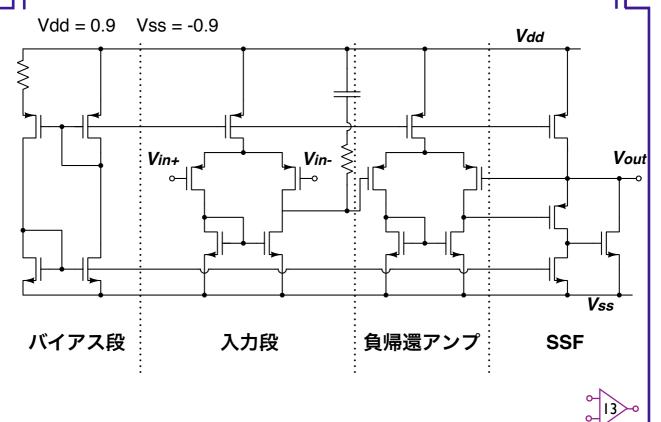

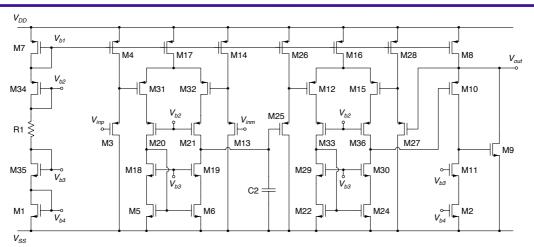

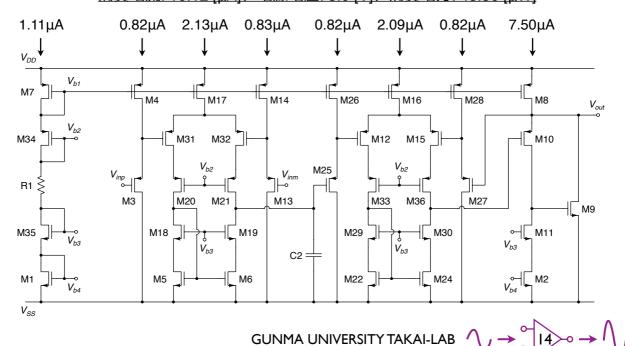

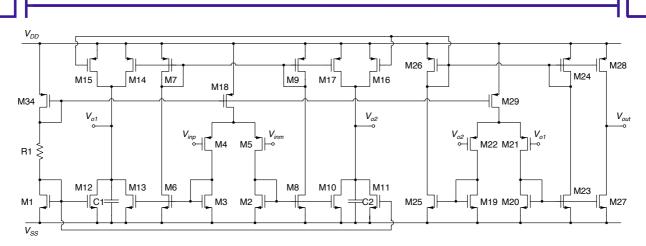

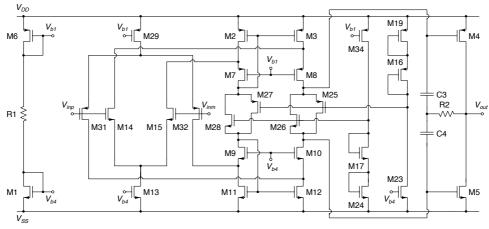

### 提出回路

V<sub>DD</sub>: 1.5 [V]、V<sub>SS</sub>: -1.5 [V]、PMOSバルク: V<sub>DD</sub>に接続、NMOSバルク: V<sub>SS</sub>に接続素子値は以下の通り。(MOSFETはLength[μm]/Width[μm])

M7, M12, M15, M20, M21, M31, M32, M33, M34, M36: 0.2/3.0

M4, M9, M14, M25, M26, M27, M28: 0.2/2.0

M1, M18, M19, M29, M30, M35: 0.2/1.0

M5, M6, M22, M24: 3.0/0.3

M3, M13: 0.2/15.0 M16, M17: 0.2/6.0 M2, M11: 0.2/3.5 M8: 0.2/16.5 M10: 0.2/10.5 R1: 850 [kΩ] C2: 0.2 [pF]

### 提出回路

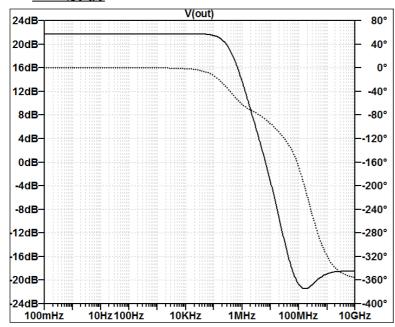

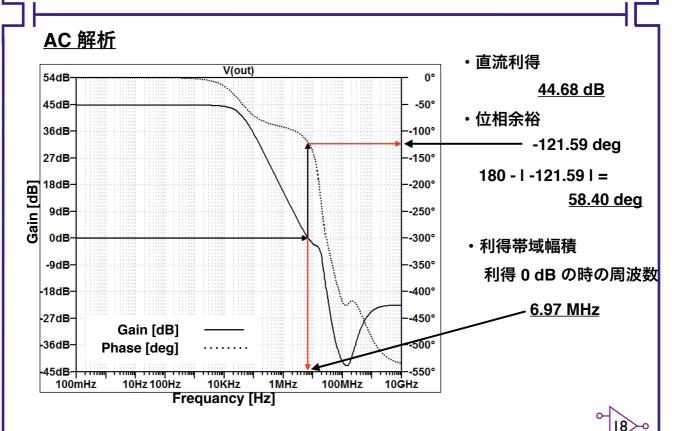

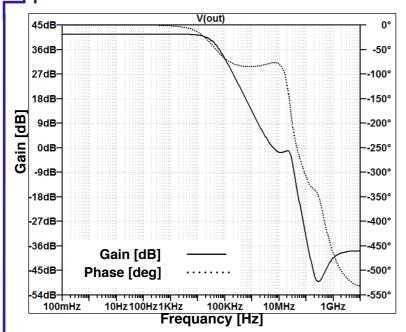

### シミュレーション結果

• 位相余裕 & 利得帯域幅積

直流利得: 66.57 [dB]、位相余裕: 73.18 [°]、利得带域幅積: 13.67 [MHz]

### シミュレーション結果

### • 出力抵抗

シミュレーションの結果は特性を評価する回路を含めた結果。 →オペアンプ単体の特性は補正計算を行う必要がある。

補正計算には公式ページの便利ツール(<u>http://ec-opamp.ce.titech.ac.jp/opcon/tools/dcgain\_ro\_corrector.cgi</u>)を使用。

シミュレーションでの直流利得: 66.57 [dB] シミュレーションでの出力抵抗: 5.238E-05 [Ω]

--- Transfer Function --

Transfer\_function: 2.00224 transfer

vin#Input\_impedance: 1e+020 impedance

output\_impedance\_at\_V(out): 5.23755e-005 impedance

実際の直流利得: 67.57 [dB] 実際の出力抵抗: 0.05585 [Ω]

### シミュレーション結果

•消費電力

消費電流: 16.12 [μA]、電源電圧: 3.0 [V]、消費電力: 48.36 [μW]

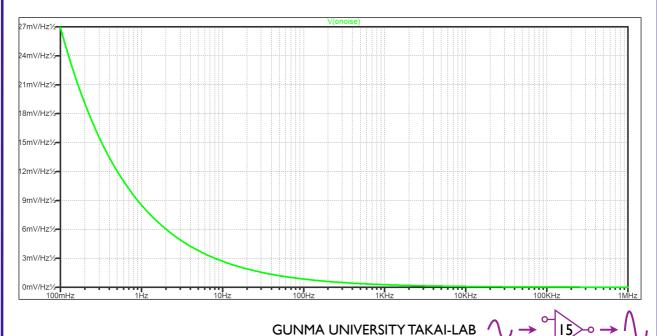

### シミュレーション結果

• 入力換算雑音

### 部門2 スコア

| 項目          | 評価値          |

|-------------|--------------|

| 消費電力 [W]    | 4.8419E+05 △ |

| 出力抵抗 [Ω]    | 1.0000E-01 O |

| 入力換算雑音 [V]  | 1.7011E-02 × |

| 利得帯域幅積 [Hz] | 1.3551E+07 〇 |

| 位相余裕 [deg]  | 6.6737E+01 🔾 |

| スコア         | 2.2677E+20   |

- ・出力抵抗を最小値である $0.1\Omega$  で設計できた。

- ・電源電圧を下げて設計を行う ことで、更に消費電力を小さ くできた可能性有り。

- ・入力換算雑音が例年の入賞回 路に比べて大きくなってし まった。

・評価式で見る部門3

部門3の得点評価式は(1)式。

電源電圧変動除去比と同相除去比を変形すると(2)式になる。どちらも直流利得(差動利得)に比例して大きくなる。

(2)式をまとめると(3)式になる。

$$得点 = \frac{ 電源電圧変動除去係数}{ 同相利得 \times 電源電圧}$$

(3)

GUNMA UNIVERSITY TAKAI-LAB  $\longrightarrow$  18  $\longrightarrow$   $\longrightarrow$  1

- ・評価式で見る部門3

- つまり、部門3で高得点を取るためには、

- 1. 電源電圧変動除去係数を大きくする。

- 2. 同相利得を小さくする。

- 3. 電源電圧を下げる。

- ことが重要となる。

電源電圧変動除去係数 × 直流利得 × 同相利得

得点 =  $\frac{\text{问相例符}}{\text{直流利得}^2 \times$ 電源電圧

### 設計方針

- ・部門3の回路設計方針

- 1. 同相利得を小さくする。

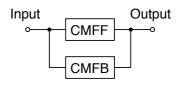

- →CMFB回路とCMFF回路の組み合わせ。

- 2. 電源電圧を下げる

- →3.0Vから1.8Vに。

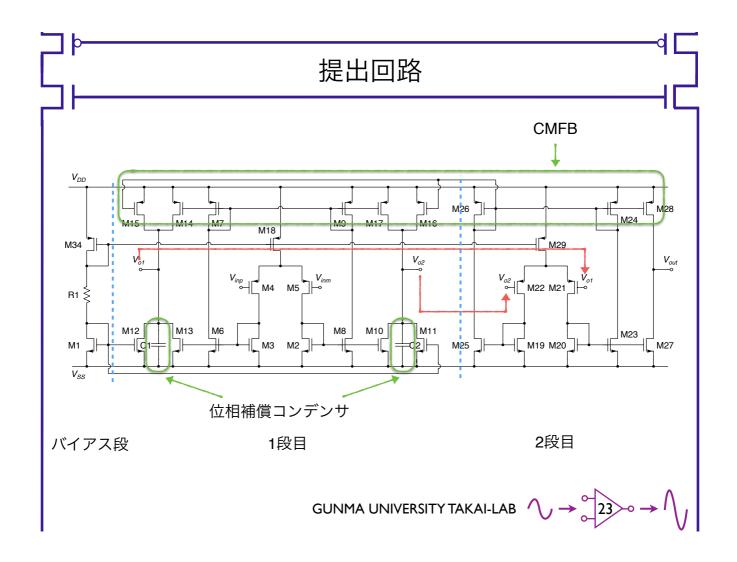

### CMFB (Common Mode FeedBack) 回路

増幅段の出力の同相信号を検出し、それを入力に返して 一定の電圧に収まるように制御する回路。

CMFF (Common Mode FeedForward) 回路

増幅段でそもそも同相信号を出力に伝えないように制御 する回路。

(2)

参考にした論文

https://www.researchgate.net/publication/2982201 A fully balanced pseudo-differential OTA with common-mode feedforward and inherent common-mode feedback detector

- ・部門3の回路設計方針

- 1. 同相利得を小さくする。

- →CMFB回路とCMFF回路の組み合わせ。

- 2. 電源電圧を下げる

- →3.0Vから1.8Vに。

コンテスト標準の電源電圧3.0V ( $\pm$ 1.5V) から、元々のプロセスパラメータ標準の電源電圧1.8V ( $\pm$ 0.9V) で動作するように設計。

→3.0/1.8≒1.67 なので他の特性が同じであれば約1.67倍のスコア向上。

GUNMA UNIVERSITY TAKAI-LAB  $\longrightarrow \bigcirc$  21  $\longrightarrow$   $\longrightarrow$   $\bigcirc$  21  $\longrightarrow$   $\longrightarrow$

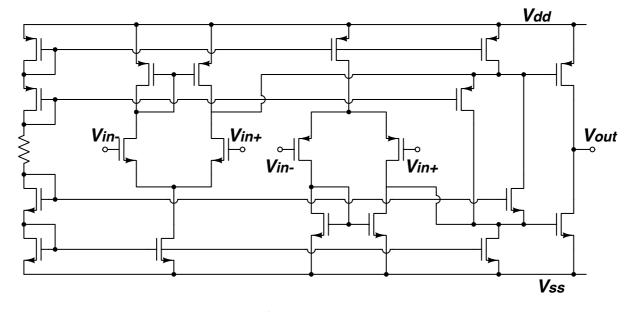

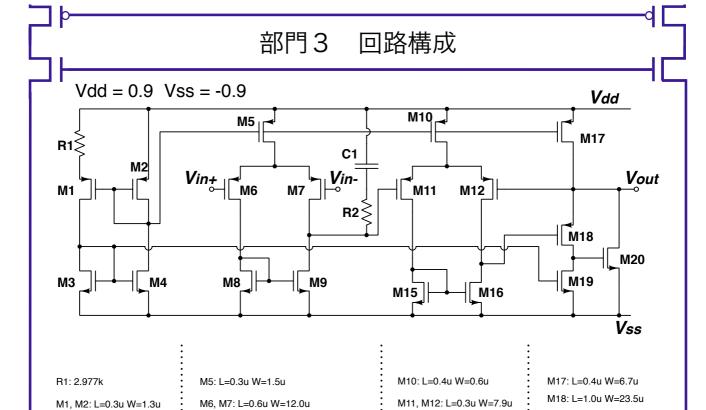

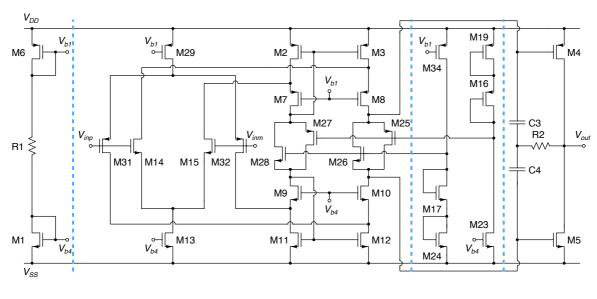

### 提出回路

$V_{DD}$ : 0.9 [V]、 $V_{SS}$ : -0.9 [V]、PMOSバルク:  $V_{DD}$ に接続、NMOSバルク:  $V_{SS}$ に接続素子値は以下の通り。(MOSFETはLength [ $\mu$ m])

M1, M2, M3, M6, M8, M10, M11, M12, M13: 1.0/3.0 M7, M9, M14, M15, M16, M17: 1.0/9.0

M19, M20, M23, M25: 1.0/1.5

M24, M26: 1.0/4.5 M4, M5: 0.2/1.8 M21, M22: 0.2/0.9 M29, M34: 10.0/90.0 M18: 10.0/180.0

M27: 1.0/16.6 M28: 1.0/45.0 C1, C2: 3.0 [pF]

R1: 148.726 [kΩ]

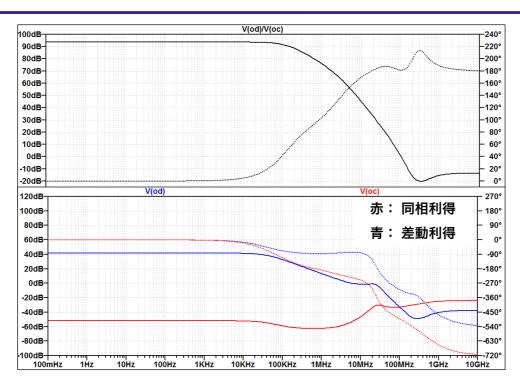

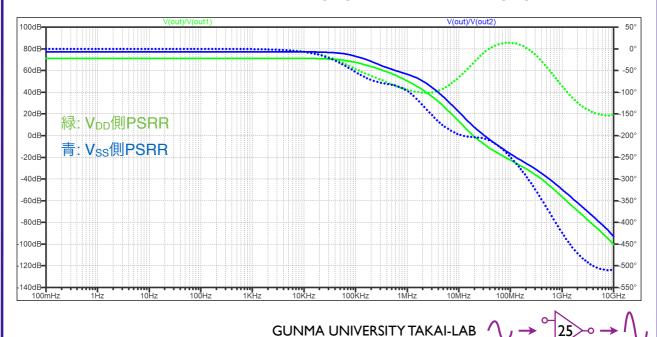

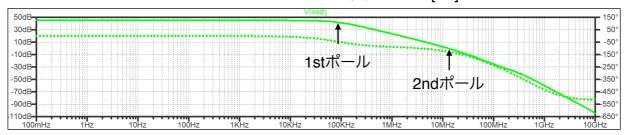

### シミュレーション結果

• 同相除去比(CMRR)

0.1Hz時 差動利得: 45.05 [dB]、同相利得: -104.99 [dB]、CMRR: 150.04 [dB]

GUNMA UNIVERSITY TAKAI-LAB

### シミュレーション結果

• 電源電圧変動除去比(PSRR)

0.1Hz時 V<sub>DD</sub>側PSRR: 71.20 [dB]、V<sub>SS</sub>側PSRR: 77.20 [dB]

### シミュレーション結果

• 直流利得

シミュレーションでの直流利得: 45.05 [dB]

シミュレーションでの出力抵抗: 204.69 [Ω]

--- Transfer Function --

Transfer\_function: 1.97789 transfer

vin#Input\_impedance: 1e+020 impedance

output\_impedance\_at\_V(out): 204.693 impedance

<u>実際の直流利得: 67.61 [dB]</u>

実際の出力抵抗: 2.484E+05 [Ω]

GUNMA UNIVERSITY TAKAI-LAB  $0 \rightarrow 0$  26  $0 \rightarrow 0$

### 部門3 スコア

| 項目             | 評価値          |

|----------------|--------------|

| 電源電圧変動除去比 [dB] | 7.1205E+01 △ |

| 同相除去比 [dB]     | 2.3322E+02 🔘 |

| 直流利得 [dB]      | 6.7514E+01 🔘 |

| 電源電圧 [V]       | 1.8000E+00 ( |

| スコア            | 1.6390E+08   |

- ・設計方針通りに同相利得を小 さくし、CMRRを大きくする ことができた。

- 電源電圧を標準の3V→1.8Vに 低電圧化し、スコアを向上さ せられた。

- PSRRを大きくする工夫ができなかった。

#

GUNMA UNIVERSITY TAKAI-LAB

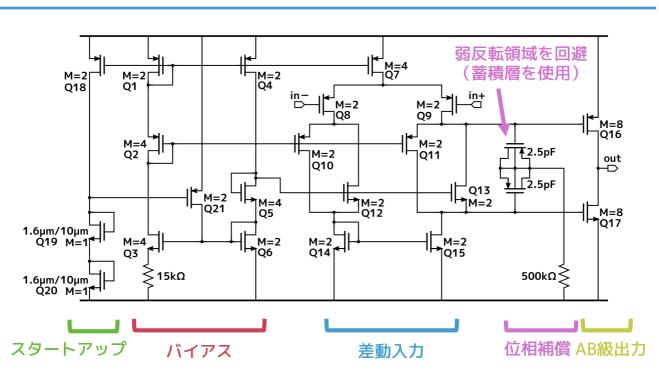

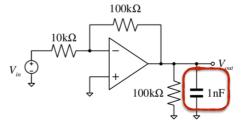

・部門4の回路設計方針

部門4の評価は消費電流がそのまま得点となる。

最低要項を満たしつつ、トレードオフとなるスルーレートをギリギリで設計し、消費電流を下げる。

ただし1nFの容量性負荷を駆動する必要があり、スルーレートが取りにくい。

時間が無かったため回路構成は研究室で行ったチップの試作で設計したものとし、素子値を少し変更して提出。

(元々今年は試作の部がなくなり、自分の設計したい回路を作っていたので、 消費電流を特に考慮した回路構成ではない。)

### 提出回路

$V_{DD}$ : 1.5 [V]、 $V_{SS}$ : -1.5 [V]、PMOSバルク:  $V_{DD}$ に接続、NMOSバルク:  $V_{SS}$ に接続素子値は以下の通り。

PMOS (L=0.8 [μm], W=9.0 [μm]) M16, M19, M25, M27, M31, M32, M34: M=1

M6, M7, M8, M29: M=2

M2, M3: M=4 M4: M=5 NMOS (L=0.8 [μm], W=3.0 [μm])

M14, M15, M17, M23, M24, M26, M28: M=1

M1, M9, M10, M13: M=2

M11, M12: M=4

M5: M=5

R1: 330 [k $\Omega$ ], R2: 550 [k $\Omega$ ], C3: 0.5 [pF], C4: 0.5 [pF]

### 提出回路

バイアス段

Rail to Rail 折り返しカスコード増幅段

AB級

AB級

バイアス段

出力段

GUNMA UNIVERSITY TAKAI-LAB  $\longrightarrow \bigcirc$  31  $\longrightarrow$   $\longrightarrow$

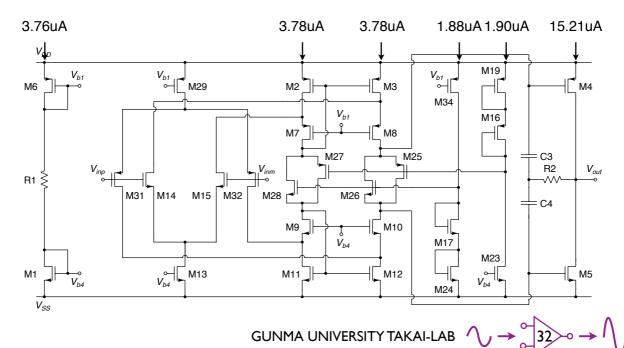

### シミュレーション結果

### 消費電流: 30.31 [uA]

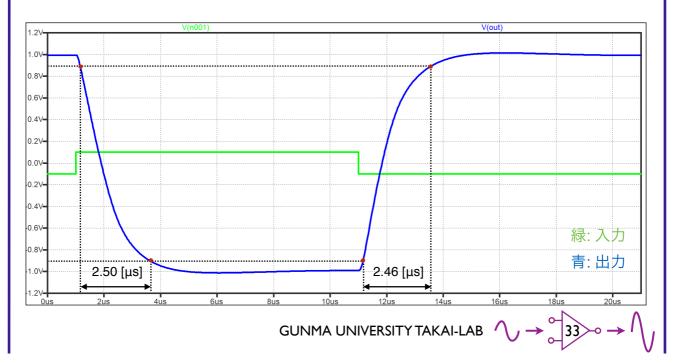

### シミュレーション結果

・スルーレート

立ち下がり: 1.8/2.50=0.720 [µV/s]、立ち上がり: 1.8/2.46=0.732 [µV/s]

### レイアウト結果

素子値は異なるものの、同じ回路構成をレイアウトした結果。(jedatのismoを使用)

### 部門4 スコア

| 項目       | 評価値        |

|----------|------------|

| 消費電流 [A] | 3.0283E-05 |

- ・デザイン部門の最低要件を満 たし、動作する回路を設計で きた。

- スルーレートをコンテストで 通るギリギリに設計しつつ、 消費電流を減らすことができ た。

GUNMA UNIVERSITY TAKAI-LAB

$$0 \rightarrow 0 \rightarrow 35 \rightarrow 0 \rightarrow 0$$

# OUTLINE OUTLINE 部門2 部門3 のしまとめ GUNMA UNIVERSITY TAKAI-LAB へ → 36 → ↑

### まとめ&感想

- ・このコンテストに参加することで、各部門ごとに特化した性能の 回路を設計する難しさを知ることができ、自身の回路設計の知識 向上やスキルアップに繋がった。

- ・最も力を入れた部門3で過去最高のスコアを取り、総合優勝でき たので良かった。

### 謝辞-

演算増幅器設計コンテスト運営の方々 協賛企業の方々、審査員の方々 このような大変貴重な機会を設けていただき、 心より感謝申し上げます。